# BTD21520x

## **Dual-Channel Isolated Gate Driver**

#### 1.Features

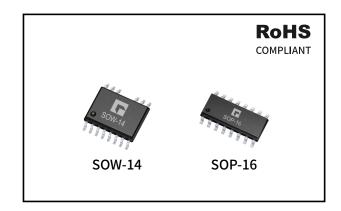

- Isolation voltage up to 5000Vrms(SOW-14)@UL1577; 3000Vrms(SOP-16)@UL1577

- Secondary-side drive voltage range up to 33V

- 4-A peak source, 6-A peak sink at output

- Integrated disable function

- Integrated dead time setting

- Typical propagation delay 45ns

- Operating temperature -40~125°C

### 2.Applications

#### Industrial:

- Power distribution

- Motor drives

- Isolated switched-mode power supplies

- Lighting systems

- · Plasma displays

- PV and industrial inverters

#### **Automotive:**

- · On-board chargers

- Battery management systems

- Charging stations

- Traction inverters

- Hybrid electric vehicles

- Battery electric vehicles

### 3.Description

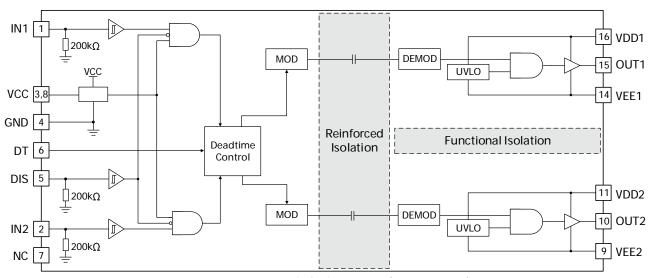

BTD21520 is an isolated dual-channel gate driver with peak 4-A source current and peak 6-A sink current. It isolates primary-side from secondary-side by a 5k Vrms reinforced isolation barrier.

Internal functional isolation between the two secondary-side output channels allows a operating voltage of up to  $1850\,V_{DC}$ . The driver can be configured as two low-side drivers, two high-side drivers, or a half-bridge driver with programmable dead time (DT). Certain models include disable (DIS) pin. When the DIS pin is set high, it shuts down both outputs simultaneously. When the DIS pin is left open or grounded, it allows the device to operate normally.

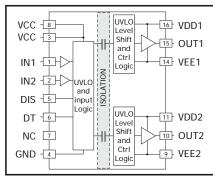

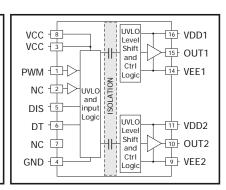

### 4. Functional Block Diagram

LIVLO 16 VDD1 VCC - 8 VCC -3 Shift 15 OUT1 and Ctrl 14- VEE1 IN1 1 Logic ISOLATION IN2 -2 luvi ol DIS input Logic UVLO NC ∰ VDD2 101 OUT2 NC and 9- VEE2 GND -4

BTD21520M BTD21520S BTD21520E

## **INDEX**

| .Features                           | 01 |

|-------------------------------------|----|

| .Applications                       | 01 |

| .Description                        | 01 |

| .Functional Block Diagram           | 01 |

| .Product Information                | 03 |

| .Pin Configuration and Functions    | 04 |

| .Specification Parameters           | 06 |

| .Parameter Testing                  | 10 |

| .Function Description               | 16 |

| 0.Applications                      | 21 |

| 1.Packaging and Packing Information | 23 |

| 2.Version Description               | 27 |

### **5.Product Information**

| Part No.     | Pin Configuration                                         | Secondary Side<br>UVLO Threshold | Operating<br>Temperature | Package | Package<br>Material | Quantity | Marking    |

|--------------|-----------------------------------------------------------|----------------------------------|--------------------------|---------|---------------------|----------|------------|

| BTD21520MAWR | Dual-channel non-inverting input, dead time configuration | 6V                               |                          |         |                     |          | BTD21520MA |

| BTD21520MBWR | and disable function                                      | 8V                               |                          |         |                     |          | BTD21520MB |

| BTD21520SAWR | Dual-channel non-inverting                                | 6V                               | -40-125°C                | SOW-14  | Tape &              | 1500pcs  | BTD21520SA |

| BTD21520SBWR | input, disable function                                   | 8V                               | -40-123 C                | 3077-14 | Reel                | /Reel    | BTD21520SB |

| BTD21520EAWR | Single PWM input, dead time                               | 6V                               |                          |         |                     |          | BTD21520EA |

| BTD21520EBWR | configuration and disable function                        | 8V                               |                          |         |                     |          | BTD21520EB |

| BTD21520MAPR | Dual-channel non-inverting input, dead time configu-      | 6V                               |                          |         |                     |          | BTD21520MA |

| BTD21520MBPR | rtion and disable function                                | 8V                               |                          |         |                     |          | BTD21520MB |

| BTD21520SAPR | Dual-channel non-inverting                                | 6V                               | -40-125°C                | SOP-16  | Tape &              | 2500pcs  | BTD21520SA |

| BTD21520SBPR | input, disable function                                   | 8V                               | -40-123 C                | SOP-16  | Reel                | /Reel    | BTD21520SB |

| BTD21520EAPR | Single PWM input, dead time configuration and disable     | 6V                               |                          |         |                     |          | BTD21520EA |

| BTD21520EBPR | function                                                  | 8V                               |                          |         |                     |          | BTD21520EB |

## **6.Pin Configuration and Functions**

### 6.1 BTD21520Mx

| NO.        | NAME         | TYPE (1)      | DESCRIPTION                                                                    | PACKAGE             |

|------------|--------------|---------------|--------------------------------------------------------------------------------|---------------------|

| 1          | IN1          | I             | Input signal for channel 1                                                     |                     |

| 2          | IN2          | I             | Input signal for channel 2                                                     |                     |

| 3          | VCC          | Р             | Primary-side supply voltage                                                    |                     |

| 4          | GND          | G             | Primary-side ground reference                                                  | IN1 10 VDD1         |

| 5          | DIS          | I             | Disables both driver outputs if asserted high, enables if set low or left open | IN2 2 15 OUT1       |

| 6          | DT           | I             | Programmable dead time function                                                | VCC 3               |

| 7          | NC           | -             | No Internal connection                                                         | GND 4<br>BTD21520Mx |

| 8          | VCC          | Р             | Primary-side supply voltage                                                    | DIS 5               |

| 9          | VEE2         | Р             | Ground for secondary-side driver 2                                             | DT 6 11 VDD2        |

| 10         | OUT2         | 0             | Output of driver 2                                                             | NC 7 10 OUT2        |

| 11         | VDD2         | Р             | Secondary-side power for driver 2                                              | VCC 8 9 VEE2        |

| 14         | VEE1         | Р             | Ground for secondary-side driver 1                                             |                     |

| 15         | OUT1         | 0             | Output of driver 1                                                             |                     |

| 16         | VDD1         | Р             | Secondary-side power for driver 1                                              |                     |

| (1) P=Powe | er, G=Ground | d, I=Input, O | =Output                                                                        |                     |

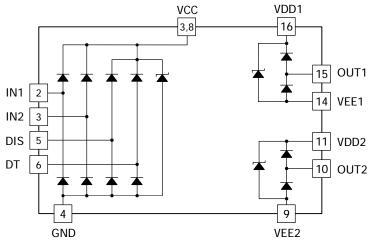

#### 6.2 BTD21520Sx

| NO. | NAME | TYPE (1) | DESCRIPTION                                                                    | PACKAGE             |        |  |

|-----|------|----------|--------------------------------------------------------------------------------|---------------------|--------|--|

| 1   | IN1  | I        | Input signal for channel 1                                                     |                     |        |  |

| 2   | IN2  | I        | Input signal for channel 2                                                     |                     |        |  |

| 3   | VCC  | Р        | Primary-side supply voltage                                                    |                     | _      |  |

| 4   | GND  | G        | Primary-side ground reference                                                  | IN1 IN              | 16 VDD |  |

| 5   | DIS  | ı        | Disables both driver outputs if asserted high, enables if set low or left open |                     | 15 OUT |  |

| 6   | NC   | -        | No Internal connection                                                         |                     | 14 VEE |  |

| 7   | NC   | -        | No Internal connection                                                         | GND 4<br>BTD21520Sx |        |  |

| 8   | VCC  | Р        | Primary-side supply voltage                                                    | DIS5                |        |  |

| 9   | VEE2 | Р        | Ground for secondary-side driver 2                                             | NC 6                | 11 VDC |  |

| 10  | OUT2 | 0        | Output of driver 2                                                             | NC 7                | 10 OUT |  |

| 11  | VDD2 | Р        | Secondary-side power for driver 2                                              | VCC 8               | 9 VEE  |  |

| 14  | VEE1 | Р        | Ground for secondary-side driver 1                                             |                     |        |  |

| 15  | OUT1 | 0        | Output of driver 1                                                             |                     |        |  |

| 16  | VDD1 | Р        | Secondary-side power for driver 1                                              |                     |        |  |

#### 6.3 BTD21520Ex

| NO.        | NAME                                     | TYPE (1) | DESCRIPTION                                                                    | PACKAGE             |  |  |  |  |  |

|------------|------------------------------------------|----------|--------------------------------------------------------------------------------|---------------------|--|--|--|--|--|

| 1          | PWM                                      | I        | PWM control signal input                                                       |                     |  |  |  |  |  |

| 2          | NC                                       | -        | No Internal connection                                                         |                     |  |  |  |  |  |

| 3          | VCC                                      | Р        | Primary-side supply voltage                                                    |                     |  |  |  |  |  |

| 4          | GND                                      | G        | Primary-side ground reference                                                  | PWM 1 16 VDD1       |  |  |  |  |  |

| 5          | DIS                                      | I        | Disables both driver outputs if asserted high, enables if set low or left open | NC 2 15 OUT1        |  |  |  |  |  |

| 6          | DT                                       | l        | Programmable dead time function                                                | VCC 3               |  |  |  |  |  |

| 7          | NC                                       | -        | No Internal connection                                                         | GND 4<br>BTD21520Ex |  |  |  |  |  |

| 8          | VCC                                      | Р        | Primary-side supply voltage                                                    | DIS 5               |  |  |  |  |  |

| 9          | VEE2                                     | Р        | Ground for secondary-side driver 2                                             | DT 6 11 VDD2        |  |  |  |  |  |

| 10         | OUT2                                     | 0        | Output of driver 2                                                             | NC 7 10 OUT2        |  |  |  |  |  |

| 11         | VDD2                                     | Р        | Secondary-side power for driver 2                                              | VCC 8 9 VEE2        |  |  |  |  |  |

| 14         | VEE1                                     | Р        | Ground for secondary-side driver 1                                             |                     |  |  |  |  |  |

| 15         | OUT1                                     | 0        | Output of driver 1                                                             |                     |  |  |  |  |  |

| 16         | VDD1                                     | Р        | Secondary-side power for driver 1                                              |                     |  |  |  |  |  |

| (1) P=Powe | (1) P=Power, G=Ground, I=Input, O=Output |          |                                                                                |                     |  |  |  |  |  |

### 7. Specification Parameters

### 7.1 Absolute Maximum Ratings

| SYMBOL          | PARAMETER                                        | MIN      | MAX      | UNIT  |

|-----------------|--------------------------------------------------|----------|----------|-------|

| VCC             | Input bias pin supply voltage (pin 3/pin 8)      | GND-0.3  | GND+6.5  |       |

| VDDx            | Driver bias supply (to VEEx)                     | VEEx-0.3 | VEEx+35  | ]     |

| Vo              | Output signal voltage                            | VEEx-0.3 | VDDx+0.3 | V     |

| V <sub>IN</sub> | Input signal voltage (INx, PWM, DIS, DT to GND)  | GND-0.3  | VCC+0.3  | ]     |

| -               | Channel to channel voltage                       | -        | 1850     |       |

| TJ              | Operating Junction Temperature                   | -40      | 150      |       |

| Ts              | Storage Temperature                              | -65      | 150      | °C    |

| T∟              | Soldering Temperature (10s)                      | -        | 300      |       |

| ESD             | Human-body model (HBM)                           | ±4       | 000      | V     |

| ESD             | Charge-device model (CDM)                        | ±1       | 500      | \ \ \ |

| -               | Input signal voltage(IN1,IN2 Transient for 50ns) | -5       | VCC+0.3  |       |

Note: The above are stress levels only. Devices are not recommended to operate under these or any other conditions beyond these values. Prolonged operation under the absolute maximum rating may affect the reliability of the device, and in severe cases it may cause permanent damage to the devices.

#### 7.2 Thermal Information

| SYMBOL                | DESCRIPTION                                  | SOW-14 | SOP-16 | UNIT  |

|-----------------------|----------------------------------------------|--------|--------|-------|

| RθJA                  | Junction-to-ambient thermal resistance       | 46.6   | 41.2   |       |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 10.5   | 7.3    |       |

| R <sub>θЈВ</sub>      | Junction-to-board thermal resistance         | 31.5   | 24.9   | °C /W |

| Ψлт                   | Junction-to-top characterization parameter   | 31.5   | 10.9   |       |

| ψлв                   | Junction-to-board characterization parameter | 41.7   | 29.2   |       |

### 7.3 Power Ratings

| SYMBOL          | PARAMETER                                          | TEST CONDITIONS                                                            | SOW-14 | SOP-16 | UNIT           |

|-----------------|----------------------------------------------------|----------------------------------------------------------------------------|--------|--------|----------------|

| P <sub>D</sub>  | Power dissipation by BTD21520x                     | VCC=5V, VDD1/2=12V, IN1/2=3.3V, 3MHz, 50% duty cycle square wave, 1nF load | 1.103  | 1.102  |                |

| P <sub>D1</sub> | Dower dissipation by each driver side of PTD21520v |                                                                            | 0.531  | 0.533  | ] <sub>w</sub> |

| P <sub>D2</sub> | Power dissipation by each driver side of BTD21520x |                                                                            | 0.561  | 0.558  | **             |

| P <sub>DI</sub> | Power dissipation by transmitter side of BTD21520x |                                                                            | 0.011  | 0.011  |                |

### 7.4 Recommended Operation Conditions

| SYMBOL          | PARAMETER                         | TEST CONDITIONS | MIN | MAX | UNIT |

|-----------------|-----------------------------------|-----------------|-----|-----|------|

| VCC             | Input supply voltage              | -               | 3   | 5   |      |

| VDDx            | Driver output bias supply         | -               | -   | 33  | V    |

| V <sub>IN</sub> | Input voltage range IN1, IN2, PWM | -               | 0   | VCC |      |

| T <sub>A</sub>  | Operating ambient temperature     | -               | -40 | 125 | °C   |

### 7.5 Safety-Limiting Values

| SYMBOL | PARAMETER                    | TEST CONDITIONS                                          |            | SIDE       | MIN | MAX  | UNIT |

|--------|------------------------------|----------------------------------------------------------|------------|------------|-----|------|------|

|        | Cafaty autout aupply aurrent | T =25°C T = 150°C                                        | VDD1/2=12V | OUT1, OUT2 | -   | 75   | m A  |

| Is     | Safety output supply current | T <sub>A</sub> =25°C , T <sub>J</sub> = 150°C            | VDD1/2=25V | OUT1, OUT2 | -   | 36   | mA   |

|        |                              | VDD1/2=25V, T <sub>A</sub> =25°C , T <sub>J</sub> =150°C |            | INPUT      | -   | 50   |      |

|        | Safety supply power          |                                                          |            | OUT1       | -   | 900  |      |

| Ps     |                              |                                                          |            | OUT2       | -   | 900  | mW   |

|        |                              |                                                          |            | TOTAL      | -   | 1850 |      |

| Ts     | Safety temperature (1)       |                                                          |            |            | -   | 150  | °C   |

<sup>(1)</sup> The maximum safety temperature, Ts, has the same value as the maximum junction temperature, TJ, specified for the device. The Is and Ps parameters represent the safety current and safety power respectively. The maximum limits of Is and Ps should not be exceeded. These limits vary with the ambient temperature, TA.

#### 7.6 Electrical Characteristics

$T_{A}\text{=-40}\sim125^{\circ}\text{C}\text{ , VCC=3.3 or 5V, VDD1=VDD2=12V, }C_{L}\text{}^{(1)}\text{=-100pF.Output pin: current towards outside of the chip is positive direction; Input pin: current towards inside of the chip is positive direction.}$

| SYMBOL                | PARAMETER                                                                          |               | TEST CONDITIONS                               | MIN | TYP | MAX | UNIT |

|-----------------------|------------------------------------------------------------------------------------|---------------|-----------------------------------------------|-----|-----|-----|------|

|                       |                                                                                    | Input Ch      | aracteristics                                 |     | l.  |     |      |

| V <sub>IH</sub>       | Input logic 1 (INx, DIS, PWM)                                                      |               | VCC=5V                                        | 2.1 | 2.4 | 2.7 |      |

| VIL                   | Input logic 0 (INx, DIS, PWM)                                                      |               | -                                             | 1.1 | 1.4 | 1.7 | V    |

| V <sub>IN_HYS</sub>   | Input Hysteresis                                                                   |               | -                                             | -   | 1   | -   |      |

| Ivcc                  | VCC quiescent current                                                              |               | -                                             | -   | 1.5 | 2   | A    |

| I <sub>VDDx</sub>     | VDDx quiescent current                                                             |               | -                                             | -   | 1   | 1.8 | mA   |

|                       | Pri                                                                                | imary side UV | LO Thresholds (VCC)                           |     |     |     |      |

| V <sub>ON1</sub>      | Rising threshold                                                                   |               | -                                             | -   | 2.6 | -   |      |

| V <sub>OFF1</sub>     | Falling threshold                                                                  |               | -                                             | -   | 2.5 | -   | V    |

| V <sub>UV, HYS1</sub> | Threshold hysteresis                                                               |               | -                                             | -   | 0.1 | -   | ]    |

|                       | Seco                                                                               | ndary side U\ | /LO Thresholds (VDDx)                         |     | •   | ,   | ,    |

| V <sub>ON2</sub>      | Rising threshold                                                                   |               | -                                             | -   | 6   | 6.3 |      |

| V <sub>OFF2</sub>     | Falling threshold                                                                  | 3TD21520xAx   | -                                             | 5.4 | 5.7 | -   |      |

| V <sub>UV, HYS2</sub> | Threshold hysteresis                                                               |               | -                                             | -   | 0.3 | -   | V    |

| V <sub>ON2</sub>      | Rising threshold                                                                   |               | -                                             | -   | 8.7 | 9.2 | V    |

| V <sub>OFF2</sub>     | Falling threshold                                                                  | BTD21520xBx   | -                                             | 7.8 | 8.2 | -   |      |

| V <sub>UV, HYS2</sub> | Threshold hysteresis                                                               |               | -                                             | -   | 0.5 | -   |      |

|                       |                                                                                    | Output C      | haracteristics                                |     |     |     |      |

| Іон                   | Peak output source current                                                         |               | C <sub>VDD</sub> =10μF,                       | -   | 4   | -   |      |

| I <sub>OL</sub>       | Peak output sink current                                                           |               | C <sub>LOAD</sub> =0.18µF, f=1kHz             | -   | 6   | -   | А    |

| I <sub>VTS</sub>      | OUTx pin reverse sinking tolerance                                                 |               | 1us pulse                                     | -   | 5   | -   |      |

| VDD-V <sub>o</sub>    | Output voltage at high state                                                       |               | I <sub>OUT</sub> =10mA                        | -   | 60  | -   | mV   |

| Vo-VEE                | Output voltage at low state                                                        |               | I <sub>OUT</sub> =-10mA                       | -   | 5.5 | -   | IIIV |

| Rонх                  | Output resistance at high state                                                    |               | I <sub>OUT</sub> =10mA, T <sub>A</sub> =25°C  | -   | 6.5 | -   | 0    |

| Rolx                  | Output resistance at low state                                                     |               | I <sub>OUT</sub> =-10mA, T <sub>A</sub> =25°C | -   | 0.5 | -   | 7.7  |

|                       |                                                                                    | Active Pull-  | Down Function                                 |     |     |     |      |

| Voutsd                | Active pull-down function, the voltage v pin to VEEx pin in event of loss of power |               | I <sub>OUT</sub> =-1A, VDDx=floating          | -   | 2.5 | -   | V    |

#### (Continued)

|                         |                                        | Switching                       | g Parameters                                   |     |     |                      |       |

|-------------------------|----------------------------------------|---------------------------------|------------------------------------------------|-----|-----|----------------------|-------|

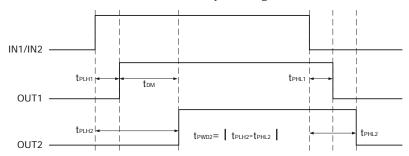

| t <sub>PLH</sub>        | Propagation delay from INx to OUTx ri  | sing edges                      | -                                              | -   | 40  | -                    | 20    |

| t <sub>PHL</sub>        | Propagation delay from INx to OUTx fa  | alling edges                    | -                                              | -   | 45  | -                    | ns    |

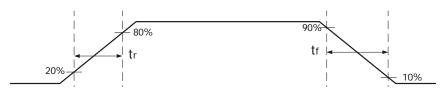

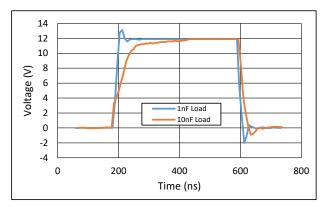

| t <sub>r</sub>          | Output rise time                       |                                 | C <sub>L</sub> =1nF, 20% to 80%                | -   | 10  | 26                   |       |

| t <sub>f</sub>          | Output fall time                       |                                 | C <sub>L</sub> =1nF, 90% to 10%                | -   | 10  | 26                   | 200   |

| t <sub>PWD</sub>        | Pulse width distortion  tphl-tplh      |                                 | -                                              | -   | -   | 10                   | ns    |

| t <sub>DM</sub>         | Propagation delays matching between    | n VOUT1, VOUT2                  | f=100kHz, IN1=IN2                              | -   | -   | 5                    |       |

| -                       |                                        |                                 | DT pull up to VCC                              |     |     | nnels are<br>pendent | -     |

| DT                      | Dead time                              | DT pin open (not recommended)   | -                                              | 8   | 15  |                      |       |

|                         |                                        |                                 | $R_{DT}=20k\Omega$                             | 160 | 200 | 250                  |       |

| t <sub>sk</sub>         | Delay variation between samples        | Delay variation between samples |                                                | -   | 1   | 25                   | ns    |

|                         | Undervoltage legicout recovery time    | tvcc+ to out                    | -                                              | -   | 40  | -                    |       |

| _                       | Undervoltage lockout recovery time     | t <sub>VDD+ to OUT</sub>        | -                                              | -   | 50  | -                    | μs    |

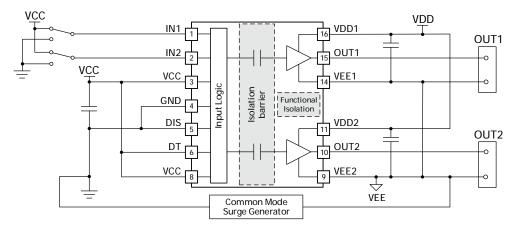

| CMTI                    | Common-mode transient immunity         |                                 | INx tied to GND or VCC, $V_{\text{CM}}$ =1500V | 100 | -   | -                    | kV/μs |

| (1) C <sub>L</sub> :Loa | ad capacitance from output pin OUTx to | o VEEx.                         |                                                |     |     |                      |       |

#### 7.7 SAFETY PARAMETERS

### 7.7.1 WIDE-BODY PACKAGE (SOW-14)

| Symbol            | PARAMETER                                 | ARAMETER TEST CONDITIONS                                                                                                                                              |                 | TYP | MAX | UNIT            |  |

|-------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----------------|--|

| CLR               | External clearance                        | Shortest pin-to-pin distance through air                                                                                                                              | 8.5             | -   | -   |                 |  |

| CPG               | External creepage                         | Shortest pin-to-pin distance across the package surface                                                                                                               | 8.5             | -   | -   | mm              |  |

| DTI               | Distance through insulation               | Minimum internal gap (internal clearance) of the double insulation (2×8.5 μm)                                                                                         | 17              | -   | -   | μm              |  |

| CTI               | Comparative tracking index                | DIN EN 60112                                                                                                                                                          | 600             | -   | -   | V               |  |

| _                 | Overvoltage category                      | Voltage rating < 600Vrms                                                                                                                                              | 1-111           | -   | -   |                 |  |

| -                 | Overvoltage category                      | Voltage rating < 1000Vrms                                                                                                                                             | 1-11            | 1   | -   | _               |  |

| $V_{IORM}$        | Maximum repetitive peak isolation voltage | AC voltage (bipolar)                                                                                                                                                  | 2121            | -   | -   | V <sub>PK</sub> |  |

| V <sub>IOWM</sub> | Maximum working isolation voltage         | AC voltage (sine wave); time dependent dielectric breakdown                                                                                                           | 1500            | -   | -   | Vrms            |  |

| V <sub>ІОТМ</sub> | Maximum transient isolation voltage       | 100% V <sub>ІОТМ</sub> , 60s, 120% V <sub>ІОТМ</sub> , 1s                                                                                                             | 7000            | -   | -   | V <sub>PK</sub> |  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage           | IEC 62368-1, 1.2/50us waveform, 1.6 x V <sub>IOSM</sub>                                                                                                               | 8000            | -   | -   | 1               |  |

|                   |                                           | Method a, After Input/Output safety test subgroup 2/3.V <sub>IN</sub> = V <sub>IOTM</sub> , 60s, V <sub>pd</sub> =1.2 V <sub>IOTM</sub> , 10s                         | -               | -   | 5   |                 |  |

| $Q_{\text{pd}}$   | Apparent charge                           | Method a, After environmental tests subgroup 1. $V_{\text{IN}}=V_{\text{IOTM}}$ , 60s, $V_{\text{pd}}=1.6V_{\text{IOTM}}$ , 10s                                       | -               | -   | 5   | рС              |  |

|                   |                                           | Method b1; At routine test (100% production) and preconditioning (type test) V <sub>IN</sub> =1.2V <sub>IOTM</sub> , 1s, V <sub>pd</sub> =1.875V <sub>IOTM</sub> , 1s | -               | -   | 5   |                 |  |

| Cıo               | Barrier capacitance, input to output      | V <sub>IO</sub> =0.4V <sub>peak</sub> , f=1MHz, sine wave                                                                                                             | -               | 1.2 | -   | pF              |  |

|                   |                                           | Test voltage of 500V, T <sub>A</sub> =25°C                                                                                                                            | 1012            | 1   | -   |                 |  |

| R <sub>IO</sub>   | Isolation resistance, input to output     | Test voltage of 500V, 100°C < T <sub>A</sub> < 125°C                                                                                                                  | 1011            | -   | -   | Ω               |  |

|                   |                                           | Test voltage of 500V, T <sub>A</sub> =150°C                                                                                                                           | 10 <sup>9</sup> | -   | -   |                 |  |

| -                 | Pollution degree                          | -                                                                                                                                                                     | -               | 2   | -   | -               |  |

| $V_{\text{ISO}}$  | Withstand isolation voltage               | $V_{\text{TEST}}=V_{\text{ISO}}=5000 \text{Vrms}$ , t=60 sec(qualification), $V_{\text{TEST}}=1.2 \times V_{\text{ISO}}=6000 \text{Vrms}$ , t=1 sec(100% production)  |                 | -   | -   | Vrms            |  |

### 7.7.2 Safety-Related Certifications (SOW-14)

| UL                                                        | VDE                                                                                                                                                                              | cQc                                                              |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| Recognized under UL 1577<br>Component Recognition Program | Plan to certify according to DIN V VDE<br>V0884-11:2017-01 and DIN EN 61010-1                                                                                                    | Plan to certify according<br>to GB 4943.1-2011                   |  |

| Single protection, 5000 VRMS                              | Reinforced Insulation<br>Maximum Transient isolation Overvoltage, 7000 Vpk;<br>Maximum Repetitive Peak Isolation Voltage, 2121 Vpk;<br>Maximum Surge Isolation Voltage, 8000 Vpk | Reinforced Insulation,<br>Altitude ≤ 5000 m,<br>Tropical Climate |  |

### 8. Parameter Testing

#### 8.1 Propagation Delay and Pulse Width Distortion

The figure below shows the characterization of pulse width distortion ( $t_{PWD}$ ) and delay matching ( $t_{DM}$ ). During the test, both inputs are in phase, the dead time function is disabled by shorting the DT Pin to VCC.

Figure 1. Dead Time Disabled, IN1 and IN2 with synchronized signal

#### 8.2 Rise Time and Fall Time

Figure 2. Definition of Rise Time and Fall Time

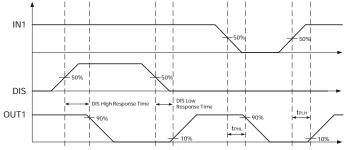

#### 8.3 Input and Disable Response Time

When the DIS pin is connected to the controller at a certain distance, it is recommended to configure a bypass capacitor of about 1nF with low stray inductance close to the DIS pin.

Figure 3. Disable Pin Timing

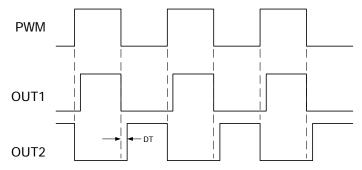

#### 8.4 Programmable Dead Time

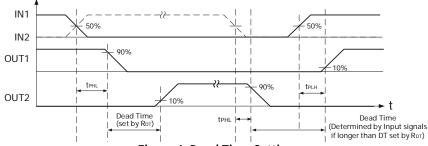

DT pin left open or connected to GND via resistor  $R_{DT}$  sets dead time between two channels.

Figure 4. Dead Time Setting

#### 8.5 CMTI Testing

Figure 5. Simplified CMTI Test Setup

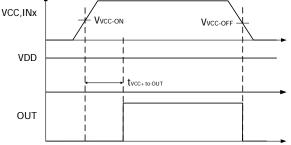

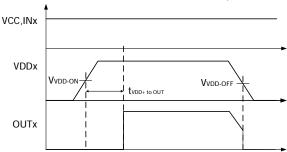

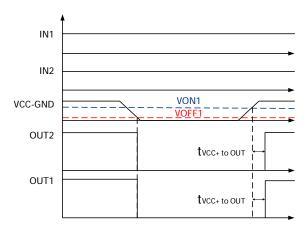

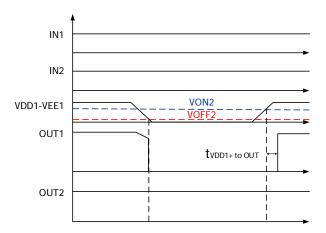

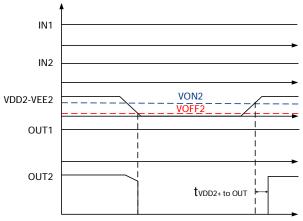

#### 8.6 UVLO Delay During IC Power-On

At the process of device power-on, there is a time delay from the start of the supply voltage rise to the UVLO recovery threshold, and then to the device output response, as shown in the figures below.  $t_{VCC^+ to OUT}$  is primary side power-on UVLO delay (typical value  $40\mu s$ ), and  $t_{VDD^+ to OUT}$  is secondary side power-on UVLO delay (typical value 50us). It is suggested that after powering on the driver IC, adequate time margin is reserved before sending PWM signal to IC.

If IN1 or IN2 is already at high level before VCC or VDDx reaches the recovery threshold, after tvcc+ to OUT or tvDD+ to OUT counting from the time point when VCC or VDDx reaches the recovery threshold, the corresponding output will jump to a high level. However, when the VCC or VDDx voltage drops to the UVLO lockout threshold, the output will be completely blocked within 1us. This asymmetric design is to ensure safe operation of a VCC or VDDx in the event of a power failure.

Figure 6. UVLO delay when the VCC is powered on

Figure 7. UVLO delay when the VDDx is powered on

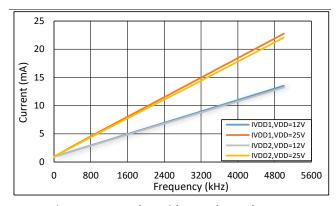

### 8.7 Typical Characteristics

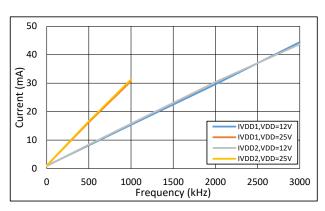

Figure 8. Secondary side per channel current consumption vs frequency (No Load, VDDx = 12 V or 25 V)

Figure 9. Secondary side per channel current consumption vs frequency (1-nF Load, VDDx = 12 V or 25 V)

Figure 10. Secondary side per channel current consumption vs frequency (10-nF Load, VDDx = 12 V or 25 V)

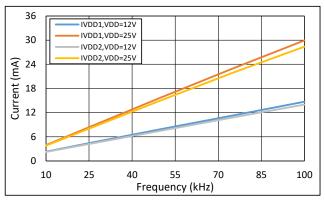

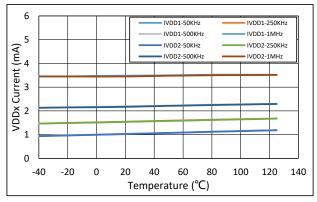

Figure 11. Secondary side per channel supply current

Vs. temperature

(No load, Different switching frequencies)

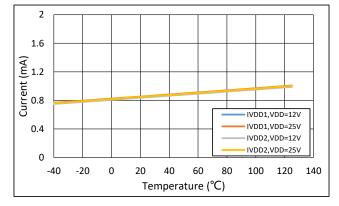

Figure 12. Secondary side per channel quiescent supply current vs temperature (No load, input low, no switching)

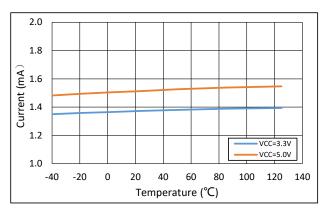

Figure 13. Primary side quiescent supply current vs temperature

(No load, input low, no switching)

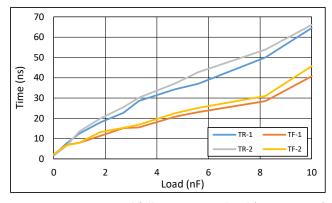

Figure 14. Rising and falling times vs load (VDDx = 12 V)

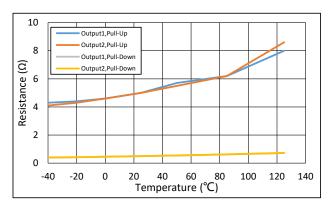

Figure 15. Output resistance vs temperature

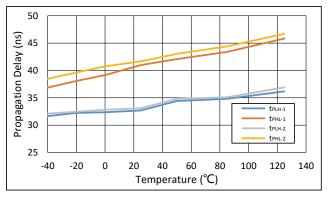

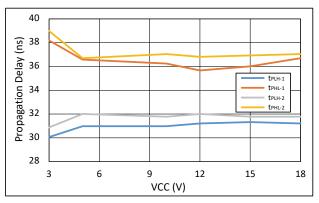

Figure 16. Propagation delay vs temperature

Figure 17. Propagation delay vs VCC

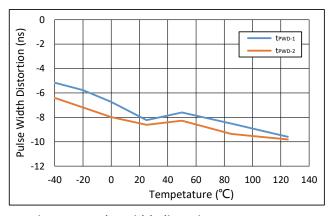

Figure 18. Pulse width distortion vs temperature

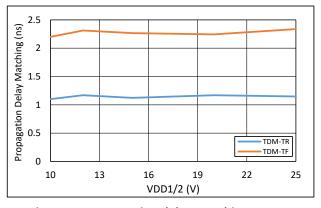

Figure 19. Propagation delay matching vs VDDx

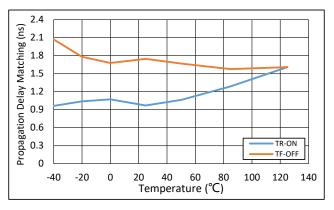

Figure 20. Propagation delay matching vs temperature

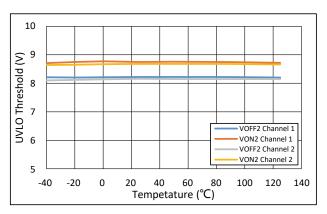

Figure 21. VDDx 8-V UVLO hysteresis vs temperature

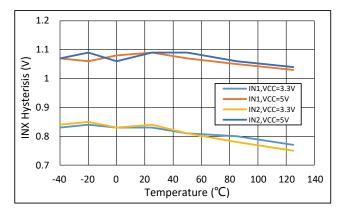

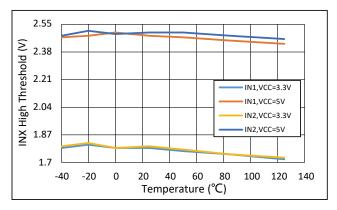

Figure 22. INx hysteresis vs temperature

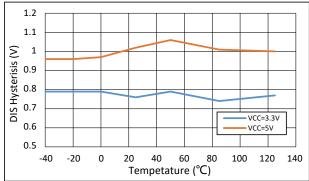

Figure 23. DIS hysteresis vs temperature

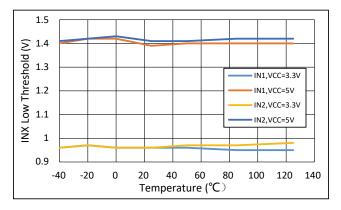

Figure 24. INx low threshold vs temperature

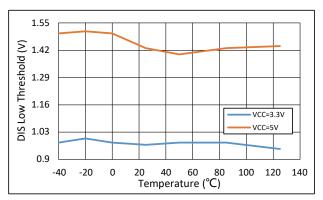

Figure 25. DIS low threshold vs temperature

Figure 26. INx high threshold vs temperature

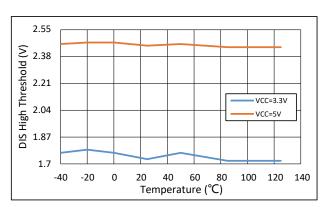

Figure 27. DIS high threshold vs temperature

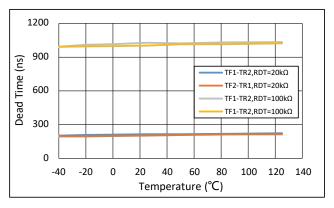

Figure 28. Dead time vs temperature

Figure 29. Typical output waveforms

## **9.Function Description**

## 9.1 Block Diagram

Figure 30. Functional Block Diagram (BTD21520Mx)

### 9.2 Input and Output Logic Table

When VCC and VDD are powered on, the relevant input and output logic information is as follows:

#### BTD21520M

| INPUT     |           | DIS            | OUTPUT |      | DESCRIPTION                                                  |

|-----------|-----------|----------------|--------|------|--------------------------------------------------------------|

| IN1       | IN2       | DIS            | OUT1   | OUT2 | DESCRIPTION                                                  |

| L         | L         | L or left open | L      | L    | If dead time function is used, output switching occurs after |

| L         | Н         | L or left open | L      | Н    | the dead time ended.See Programmable Dead Time (DT) pin      |

| Н         | L         | L or left open | Н      | L    | DT is left open or programmed with R <sub>DT</sub>           |

| Н         | Н         | L or left open | Н      | Н    | DT pin pulled to VCC                                         |

| Left open | Left open | L or left open | Ĺ      | L    | -                                                            |

| X         | X         | Н              | Ĺ      | L    | -                                                            |

#### BTD21520S

| INPUT     |           | DIS            | OUTPUT |      | DESCRIPTION                                               |  |

|-----------|-----------|----------------|--------|------|-----------------------------------------------------------|--|

| IN1       | IN2       | D13            | OUT1   | OUT2 | DESCRIPTION                                               |  |

| L         | L         | L or left open | L      | L    |                                                           |  |

| L         | Н         | L or left open | L      | Н    | No internal dead time setting, two output channels are in |  |

| Н         | L         | L or left open | Н      | L    | pendent                                                   |  |

| Н         | Н         | L or left open | Н      | Н    |                                                           |  |

| Left open | Left open | L or left open | L      | L    | -                                                         |  |

| Х         | Χ         | Н              | L      | L    | -                                                         |  |

#### BTD21520E

| PWM INPUT                        | DIS | OUTPUT |      | DESCRIPTION                                                        |  |  |

|----------------------------------|-----|--------|------|--------------------------------------------------------------------|--|--|

| T WINTING OT                     |     | OUT1   | OUT2 | DESCRIPTION                                                        |  |  |

| Н                                | L   | Н      | L    | If dead time function is used, output jumps after dead time ended. |  |  |

| L/Left open                      | L   | L      | Н    | See Programmable Dead Time (DT) pin                                |  |  |

| X                                | Н   | L      | L    | Device disabled                                                    |  |  |

| (1) "X" means L, H or left open. |     |        |      |                                                                    |  |  |

#### 9.3 Input Stage Characteristics

With input pins and secondary side completely isolated, BTD21520 is designed to be compatible with CMOS levels, and supports 3.3V, 5V and 15V level input, making the chip easy to accept control of multiple logic levels. Inputs with Schmitt stage for improved anti-interference performance. INx, PWM, and DIS have a built-in  $200k\Omega$  resistor pulled down to the ground, ensuring that the output of the device is low when the input is left open However, in order to ensure the initial power-on state of the device, it is recommended to add an appropriate pull-up or pull-down resistor to the input.

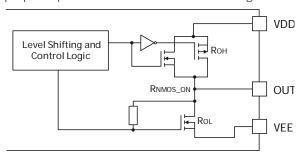

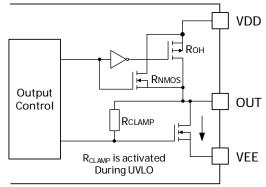

#### 9.4 Output Booster Characteristic

The BTD21520 has a rail-to-rail booster stage output. The pull-up structure of the output stage consists of a P-channel MOSFET and an N-channel MOSFET connected in parallel. At turn-on, N-channel MOSFET provides high current driving capability. P-channel MOSFET provides a small steady-state conduction voltage drop. The PMOS on-resistance ( $R_{\text{OH}}$ ) is  $6.5\Omega$ , and the NMOS on-resistance ( $R_{\text{NMOS ON}}$ ) is  $0.5\Omega$ .

The pull-down structure is implemented using an N-channel MOSFET. A  $1M\Omega$  resistor is connected in parallel between the drain and gate of the MOSFET to effectively clamp the gate voltage of the power device in the event of a loss of pow-er to prevent the occurrence of partial turn-on. However, in order to ensure reliable shutdown of the power device, it is recommended that appropriate pull-down resistor be added to the gate.

Figure 31. Output Characteristics Diagram

#### 9.5 Device Function

#### 9.5.1 Disable

When the DIS pin is set high, both outputs can be shut down at the same time. The device operates normally when the DIS pin is grounded or left open. The response time of the disable function is within 20ns. The disable function is activated or deactivated according to the input only when the VCC is kept above the undervoltage turn-on threshold. If the DIS pin is not used, it is recommended to connect it to the ground. If connecting DIS pin to a microcontroller with distance, it is recommended to bypass the DIS pin with a low ESR/ESL capacitor of approximately 1nF for better noise immunity.

#### 9.5.2 Pulling DT Pin Up to VCC

The two channels are independent, with output exactly matching input, and no dead time is inserted, allowing the output signals to be both high.

#### 9.5.3 Dead Time Setting

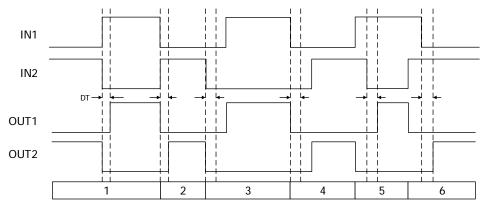

DT pin sets the dead time.It is used to set the dead time between channel 1 and channel 2 to prevent them from shoot-through. The steady-state voltage of DT pin is 0.8V, and the current value of the pin is measured for corresponding dead time. The dead time is calculated as  $t_{DT}=10\times R_{DT}$ . The unit of  $t_{DT}$  is ns and the unit of  $R_{DT}$  is  $k\Omega$ . To ensure that the pin signal is not interfered, it is recommended to place a 2.2nF capacitor near the IC between DT pin and GND, and it is not recommended to leave DT pin open.

Figure 32.Dead Time Setting

The falling edge of one input signal activates the the programmed dead time for the other signal. The dead time of the output signal is selected by IC, either the dead time set by IC itself or for the dead time of input signal itself, and the IC output chooses the longer one out of the two. If both input signals are high at the same time, both output signals are immediately set to low. This feature is intended to prevent shoot-through and does not affect the normal operation of the dead time settings. The following figure illustrates and demonstrates the various dead time logical operations.

Figure 33. BTD21520M Input and Output Logic Relationship With Input Signals

**State 1:** IN2 goes low, IN1 goes high. IN2 sets OUT2 low immediately and assigns the programmed dead time to OUT1. OUT1 is allowed to go high after the programmed dead time.

State 2: IN2 goes high, IN1 goes low. Now IN1 sets OUT1 low immediately and assigns the programmed dead time to OUT2.OUT2 is allowed to go high after the programmed dead time.

State 3: IN2 goes low, IN1 is still low.IN2 sets OUT2 low immediately and assigns the programmed dead time for OUT1. In this case, the input signal's own dead time is longer than the programmed dead time. Thus, when IN1 goes high, it immediately sets OUT1 high.

State 4: IN1 goes low, IN2 is still low. IN1 sets OUT1 low immediately and assigns the programmed dead time to OUT2. IN2's own dead time is longer than the programmed dead time. Thus, when IN2 goes high, it immediately sets OUT2 high. State 5: IN1 goes high, while IN2 and OUT2 are still high. To avoid overshoot, IN1 immediately pulls OUT1 low and keeps OUT1 low. After some time IN2 goes low and assigns the programmed dead time to OUT1. OUT2 is already low. After the programmed dead time, OUT1 is allowed to go high.

State 6: IN2 goes high, while IN1 and OUT1 are still high. To avoid overshoot, IN2 immediately pulls OUT1 low and keeps OUT2 low. After some time IN1 goes low and assigns the programmed dead time to OUT2. OUT1 is already low. After the programmed dead time, OUT2 is allowed to go high.

#### 9.5.4 BTD21520E Dead Time

A dead time elapses before OUT1 or OUT2 goes high, so as to prevent the high and low side MOSFET shoot-through.

Figure 34. Logic relationship between input and output signals of BTD21520E

#### 9.6 Protection Function

#### 9.6.1 UVLO

There is an internal undervoltage lock-out (UVLO) on the power circuit function area between VDDx and VEE pins of two out-puts. When the voltage of VDDx is below the undervoltage recovery threshold before starting, or below the undervoltage protection threshold after starting, the output will remain low regardless of the input state. When the output of the driver is in powered-off or undervoltage state, its output is clamped to the low level by the active clamping circuit, as shown in the figure below. At this time, the PMOS of the high side is blocked and high impedance, and the NMOS gate of the low side is connected to the output of the driver by the resistor R<sub>CLAMP</sub>. In the absence of bias voltage, the output is effectively clamped to the threshold voltage of the low-side NMOS device, typically around 1.5V (see Figure 35).

Figure 35. Simplified Representation of Active Pulldown Feature

The VDDx undervoltage protection has a V<sub>VDD\_HYS</sub> feature that prevents vibration in the presence of noise from the power supply to ground. This also allows the device to accept a small decrease in bias voltage when the device starts to turn on/off and the operating current consumption increases abruptly. Like the VDDx, there is also an undervoltage lock-out (UVLO) integrated on the primary side of the VCC. When the bias voltage is applied to the VCC terminal and the voltage is lower than the undervoltage turn-on threshold, the device will not be activated. After the activation of the device, if the VCC voltage continuously decreases to the undervoltage turn-off threshold, the signal will stop transmission. Like the undervoltage lockout of VDD, the undervoltage lockout of VCC also has hysteresis feature.

Figure 36. Timing Diagram of Undervoltage Lockout

Figure 37. Timing Diagram of Undervoltage Lockout

Figure 38. Timing Diagram of Undervoltage Lockout

#### 9.7 ESD Structure

The figure below shows the ESD-protected diode configuration of the input and output pins.

Figure 39. ESD Structure Diagram

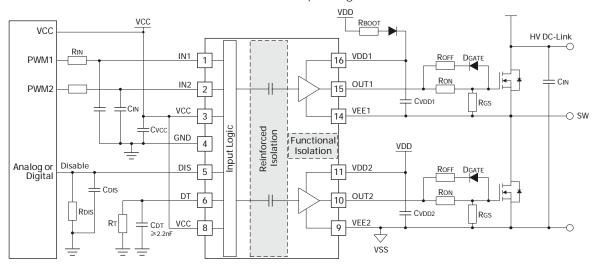

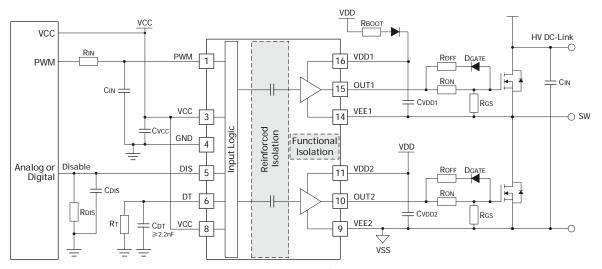

### 10.Applications

The following sections introduce the basic typical application of the driver ICs, which is for reference only. In practical application, users need to verify and test its applicability according to their own design requirements to confirm the system function.

#### **10.1 Typical Applications**

It is recommended that customers add a RC filter with a small time constant at the input port to filter out high-frequency interference without adding a large delay. It is recommended that the resistance value should be between 0 and  $100\Omega$  and the capacitance should be less than 1000pF. When setting this parameter, the influence between high frequency interference and delay needs to be taken into account.

To ensure the supply stability, It is recommended to add an appropriate capacitor between the power supply and ground. It is recommended that the primary side supply VCC-GND be connected in parallel with 1uF+ 0.1uF capacitor  $C_{VCC}$ , and the secondary side supply VDDx-VEEx be connected with  $10\mu$ F+  $0.22\mu$ F capacitors  $C_{VDD1}$  and  $C_{VDD2}$ .

The bootstrap capacitor is charged by VDD through an external bootstrap diode every cycle when the low side transistor turns on. Charging the capacitor involves high-peak currents, and therefore transient power dissipation in the bootstrap diode may be significant. Conduction loss also depends on the diode's forward voltage drop. Both the diode conduction losses and reverse recovery losses contribute to the total losses in the gate driver circuit.

The recommended value for  $R_{BOOT}$  is between 1  $\Omega$  and 20  $\Omega$  depending on the diode used.

Figure 40. BTD21520M Application Diagram

Figure 41. BTD21520E Application Diagram

### 10.2 Recommended Designs

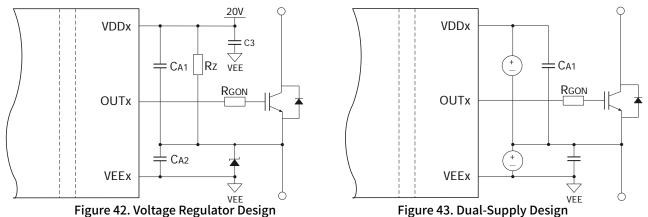

#### 10.2.1 Recommended Design of Secondary Side Supply

In order to avoid partial turn-on of the gate of the power device due to interference, it is recommended that customers add a negative supply when designing the driving output. It is recommended to use the following two methods to generate the negative supply: Use a regulator to generate stable negative voltage, or use both positive and negative supplies.

## 11. Packaging and Packing Information

### 11.1 Package Identifier

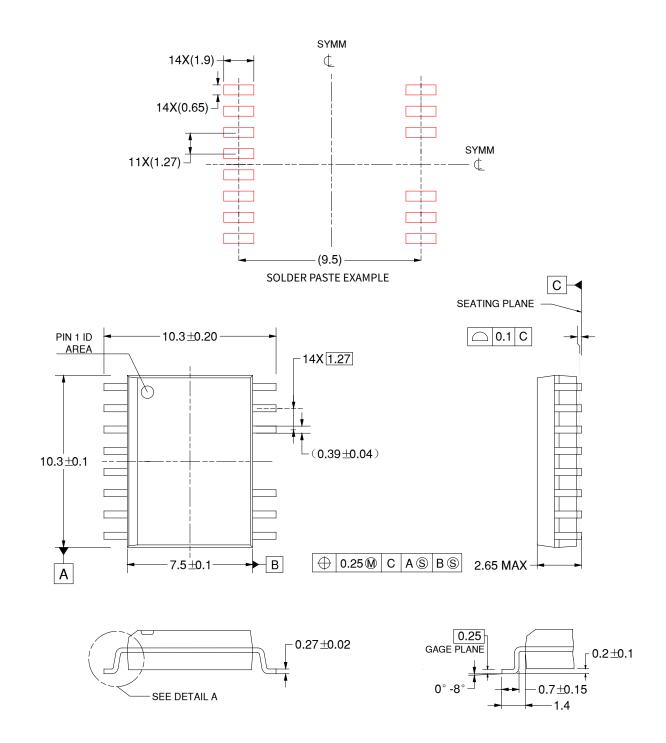

### 11.1.1 SOW-14 Package Identifier

Note: 1)Legend unit: mm.

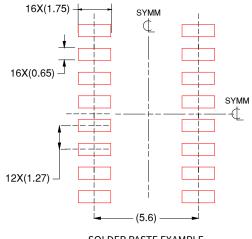

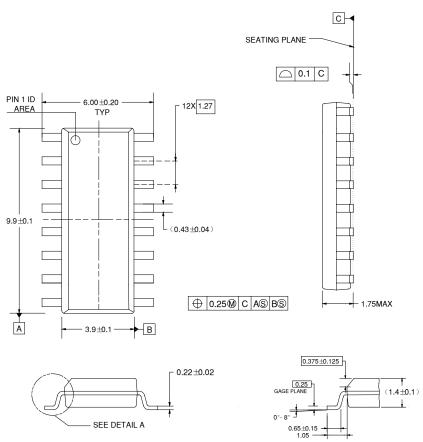

#### 11.1.2 SOP-16 Package Identifier

SOLDER PASTE EXAMPLE

Note: 1) Legend unit: mm.

#### **Electrostatic Discharge Caution**

This integrated circuit can be damaged by ESD. It is recommended that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 11.2 Packing Information

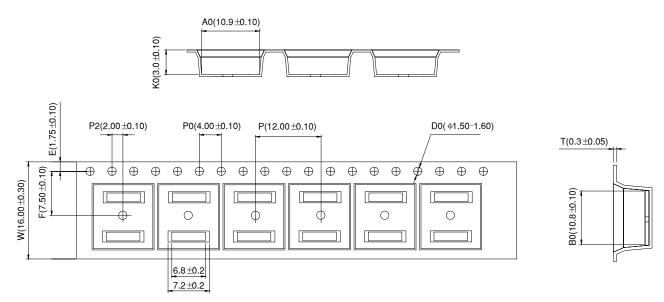

### 11.2.1 SOW-14 Packing Information

Note: 1) Legend unit: mm.

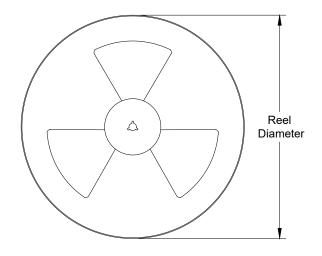

#### **REEL DIMENSIONS**

| ITEM           | FOOTPRINT |  |  |

|----------------|-----------|--|--|

| Reel Diameter  | 13 inches |  |  |

| Reel Width(W1) | 12.4mm    |  |  |

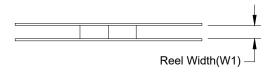

### 11.2.2 SOP-16 Packing Information

Note: 1) Legend unit: mm.

### **REEL DIMENSIONS**

| ITEM           | FOOTPRINT |

|----------------|-----------|

| Reel Diameter  | 13 inches |

| Reel Width(W1) | 16mm      |

### 12. Version Description

| REVISION | NOTES                                                    | DATE        |

|----------|----------------------------------------------------------|-------------|

| Rev.0.0  | Released datasheet                                       | 12-Jan-2023 |

| Rev.0.1  | Parameters extended and SOP-16 package information added | 15-Dec-2023 |

| Rev.0.2  | Safety certification added                               | 28-Mar-2024 |

#### IMPORTANT NOTICE AND DISCLAIMER

Bronze provides technical and reliability data(including datasheets), design resources(including 3D model, reference designs), application or other design advice, tools, safety information, and with all faults, and disclaims all warranties. Express and implied, including without limitation any implied warranties of merchantability, fitness for a particular purpose or non-infringement of third party intellectual property rights.

These resources are intended for skilled developers designing with bronze products. You are solely responsible for

- (1) selecting the appropriate bronze products for your application

- (2) designing, validating and testing your application

- (3) ensuring your application meets applicable standards.

Bronze reserves the right to modify data, texts and materials at any time, these resources are subject to change without notice. Please visit the bronze website <a href="https://www.qtjtec.com">www.qtjtec.com</a> account for the latest information. Bronze grants you permission to use these resources only for development of an application that uses the bronze products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other bronze intellectual property right or to any third party intellectual property right. For any claims, damages, losses and costs arising from using of these resources,

bronze disclaims responsibility for, and you will fully indemnify bronze and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. And bronze have the right to recover losses caused by infringement of intellectual property rights.

#### Bronze Technology Group | Shenzhen bronze Technology Co., Ltd

- © Shenzhen bronze Technology Co., Ltd

- www.qtjtec.com

- **a** +86 0755 33379866

- support@qtjtec.com

o