# BTD5350

# **Single-Channel Isolated Gate Driver**

#### 1.Features

- Isolation voltage up to 5000Vrms(SOW-8)@UL1577; 3000Vrms(SOP-8)@UL1577

- Peak output current up to 10A

- Propagation delay 60ns

- Maximum switching frequency 1MHz

- Primary-side supply 3~18V

- Secondary-side supply up to 33V

- Primary-side and secondary-side power supply undervoltage lockout (UVLO)

- Compatible with 3.3V, 5V and 15V input

- Feature Options:

Miller Clamp Options (BTD5350M)

Split Outputs (BTD5350S)

UVLO with respect to IGBT emitter (BTD5350E)

- 8-pin Package: SOP-8 with 4mm creepage SOW-8 with 8.5mm creepage

- Operating Temperature -40~125°C

## 2.Applications

- Motor drivers

- EV chargers

- · Telecommunication power supplies

- EV power supplies

- UPS

- String solar inverters

## 3.Description

BTD5350 is a family of single-channel, isolated gate driver with peak output current up to 10A, available in SOP-8 (narrow-body) or SOW-8 (wide-body) packages and supports isolation voltages up to 3000Vrms and 5000Vrms respectively. They can be used to drive IGBTs and Si/SiC MOSFETs. BTD5350 family offers 3 Feature Options:

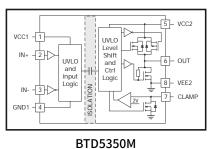

BTD5350M provides Miller clamp function to prevent false turn-on caused by Miller current.

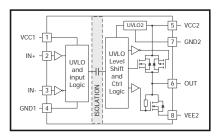

BTD5350S provides a split output with rise and fall time individually configurable.

BTD5350E provides UVLO in positive power supply of secondary-side to ensure that power devices get sufficient gate turn-on voltage.

## 4. Functional Block Diagram

VCC1 1 UVLO Level and input IN- 3 Logic OUTH Color Ctrl Color (Ctrl Color Color (Ctrl Colo

BTD5350S BTD5350E

## **INDEX**

| Features                          | . 01 |

|-----------------------------------|------|

| 2.Applications                    | . 01 |

| 3.Descriptions                    | 01   |

| I.Functional Block Diagram        | . 01 |

| j.Product Information             | . 03 |

| S.Pin Configuration and Functions | 04   |

| '.Specification Parameters        | 05   |

| 3.Parameter Testing               | . 09 |

| ).Function Description            | . 10 |

| 0.Applications                    | . 13 |

| 1.Package and Packing Information | . 15 |

| 2.Version Description             | 19   |

## **5.Product Information**

| Part No.    | Pin<br>Configuration | Isolation<br>Voltage | UVLO<br>Threshold | Operating<br>Temperature | Package | Package<br>Material | Quantity | Marking   |

|-------------|----------------------|----------------------|-------------------|--------------------------|---------|---------------------|----------|-----------|

| BTD5350MBPR |                      | 3000Vrms             | 8V                |                          | SOP-8   |                     | 2500pcs  | BTD5350MB |

| BTD5350MCPR | Millor alongo        | 300071115            | 11V               |                          | 3UP-8   |                     | /Reel    | BTD5350MC |

| BTD5350MBWR | Miller-clamp         | F000\/###            | 8V                |                          | COM 0   |                     | 1000pcs  | BTD5350MB |

| BTD5350MCWR |                      | 5000Vrms             | 11V               |                          | SOW-8   |                     | /Reel    | BTD5350MC |

| BTD5350SBPR | Calit autaut         | 2000/                | 8V                |                          | COD 0   |                     | 2500pcs  | BTD5350SB |

| BTD5350SCPR |                      | 3000Vrms             | 11V               | -40~125°C                | SOP-8   | Tape & Reel         | /Reel    | BTD5350SC |

| BTD5350SBWR | Split output         | F000\/see e          | 8V                | -40~125 C                | COM 0   |                     | 1000pcs  | BTD5350SB |

| BTD5350SCWR |                      | 5000Vrms             | 11V               |                          | SOW-8   |                     | /Reel    | BTD5350SC |

| BTD5350EBPR |                      | 3000Vrms             | 00V/rms           |                          | SOP-8   |                     | 2500pcs  | BTD5350EB |

| BTD5350ECPR | UVLO with refer-     | 300071115            | 11V               |                          | 3UP-8   |                     | /Reel    | BTD5350EC |

| BTD5350EBWR | ence to GND2         | 5000Vrms             | 8V                |                          | SOW-8   |                     | 1000pcs  | BTD5350EB |

| BTD5350ECWR |                      | SUUUVIIIS            | 11V               |                          | 3UVV-8  |                     | /Reel    | BTD5350EC |

## **6.Pin Configuration and Functions**

## 6.1 BTD5350M

| NO.        | NAME         | TYPE (1)      | DESCRIPTION                         | PACKAGE       |

|------------|--------------|---------------|-------------------------------------|---------------|

| 1          | VCC1         | Р             | Input supply voltage                |               |

| 2          | IN+          | I             | Non-inverting gate signal input pin |               |

| 3          | IN-          | I             | Inverting gate signal input pin     | VCC1 1 8 VEE2 |

| 4          | GND1         | G             | Input ground                        | IN+ 2 7 CLAMP |

| 5          | VCC2         | Р             | Positive output supply rail         | IN- 3 6 OUT   |

| 6          | OUT          | 0             | Gate-drive output                   | GND1  4 5     |

| 7          | CLAMP        | I             | Miller-clamp input                  |               |

| 8          | VEE2         | Р             | Negative output supply rail         |               |

| (1) P=Powe | er, G=Ground | d, I=Input, O | =Output                             |               |

#### 6.2 BTD5350S

| NO.        | NAME                                     | TYPE (1) | DESCRIPTION                         | PACKAGE       |  |  |  |

|------------|------------------------------------------|----------|-------------------------------------|---------------|--|--|--|

| 1          | VCC1                                     | Р        | Input supply                        |               |  |  |  |

| 2          | IN+                                      | I        | Non-inverting gate signal input pin |               |  |  |  |

| 3          | IN-                                      | 1        | Inverting gate signal input pin     | VCC1 1 8 VEE2 |  |  |  |

| 4          | GND1                                     | G        | Input ground                        | IN+ 2 7 OUTL  |  |  |  |

| 5          | VCC2                                     | Р        | Positive output supply rail         | IN- 3 6 OUTH  |  |  |  |

| 6          | OUTH                                     | 0        | Gate-Drive pullup output pin        | GND1 4 5 VCC2 |  |  |  |

| 7          | OUTL                                     | 0        | Gate-Drive pulldown output pin      |               |  |  |  |

| 8          | VEE2                                     | Р        | Negative output supply rail         |               |  |  |  |

| (1) P=Powe | (1) P=Power, G=Ground, I=Input, O=Output |          |                                     |               |  |  |  |

#### 6.3 BTD5350E

| NO.        | NAME                                     | TYPE (1) | DESCRIPTION                         | PACKAGE       |  |  |  |

|------------|------------------------------------------|----------|-------------------------------------|---------------|--|--|--|

| 1          | VCC1                                     | Р        | Input supply                        |               |  |  |  |

| 2          | IN+                                      | I        | Non-inverting gate signal input pin |               |  |  |  |

| 3          | IN-                                      | I        | Inverting gate signal input pin     | VCC1 1 8 VEE2 |  |  |  |

| 4          | GND1                                     | G        | Input ground                        | IN+ 2 7 GND2  |  |  |  |

| 5          | VCC2                                     | Р        | Positive output supply rail         | IN- 3 6 OUT   |  |  |  |

| 6          | OUT                                      | 0        | Gate-Drive pullup output pin        | GND1 4 5 VCC2 |  |  |  |

| 7          | GND2                                     | G        | Gate-Drive common pin               |               |  |  |  |

| 8          | VEE2                                     | Р        | Negative output supply rail         |               |  |  |  |

| (1) P=Powe | (1) P=Power, G=Ground, I=Input, O=Output |          |                                     |               |  |  |  |

## 7. Specification Parameters

## 7.1 Absolute Limits

| PARAMETER                                             | TEST CONDITIONS            | MIN              | MAX      | UNIT                                  |

|-------------------------------------------------------|----------------------------|------------------|----------|---------------------------------------|

| Input bias pin supply voltage                         | VCC1-GND1                  | -0.3             | 18       |                                       |

| Driver bias supply                                    | VCC2-VEE2                  | -0.3             | 35       |                                       |

| V <sub>EE2</sub> bipolar supply voltage for E version | VEE2-GND2                  | -17.5            | 0.3      | V                                     |

| Output signal voltage                                 | OUT, OUTH, OUTL, CLAMP     | VEE2-0.3         | VCC2+0.3 |                                       |

| Input signal voltage                                  | IN+, IN-                   | GND1-5           | VCC1+0.3 |                                       |

| Junction temperature, TJ                              | -                          | -40              | 150      |                                       |

| Storage temperature, T <sub>s</sub>                   | -                          | -65              | 150      | °C                                    |

| Pin soldering temperature, T∟                         | Duration < 10s             | -65 150<br>- 300 |          |                                       |

| ESD                                                   | Human-body-model (HBM)     | ±3               | 8000     | V                                     |

| ESU                                                   | Charged-device model (CDM) | ±1               | .500     | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

Note: These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability, and cause permanent damage to the device under severe conditions.

#### 7.2 Thermal Information

| SYMBOL                | PARAMETER                                    | VAI   | UNIT  |       |

|-----------------------|----------------------------------------------|-------|-------|-------|

|                       | PARAINETER                                   | SOP-8 | SOW-8 | UNII  |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 87.7  | 91.4  |       |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 19.4  | 35.1  |       |

| R <sub>θ</sub> ЈВ     | Junction-to-board thermal resistance         | 43.0  | 73.8  | °C /W |

| ψлτ                   | Junction-to-top characterization parameter   | 57.3  | 51.0  |       |

| ψյв                   | Junction-to-board characterization parameter | 65.7  | 47.7  |       |

## 7.3 Recommended Operating Conditions

| SYMBOL           | PARAMETER                                                | MIN    | MAX  | UNIT |       |

|------------------|----------------------------------------------------------|--------|------|------|-------|

| V <sub>CC1</sub> | Input supply voltage (VCC1–GND1)                         | 3      | 15   |      |       |

| W                | Total supply valtage output side (VCC2, VCC2)            | 350xCx | 13.2 | 33   |       |

| V <sub>CC2</sub> | Total supply voltage output side (VCC2–VEE2)  BTD5350xBx | 350xBx | 9.5  | 33   | \ \ \ |

| V <sub>EE2</sub> | Bipolar supply voltage for E version (VEE2–GND2)         |        | -16  | 0    |       |

| TA               | Ambient temperature                                      |        | -40  | 125  | °C    |

## 7.4 Power Ratings

| PARAMETER                                     | TEST CONDITIONS                                         | MIN | MAX  | UNIT |  |  |  |

|-----------------------------------------------|---------------------------------------------------------|-----|------|------|--|--|--|

| SOP-8                                         |                                                         |     |      |      |  |  |  |

| Maximum power dissipation on input and output | V <sub>CC1</sub> =15V, V <sub>CC2</sub> =15V, f=2.1MHz, | -   | 1.14 |      |  |  |  |

| Maximum input power dissipation               | 50% duty cycle, square wave,                            | -   | 0.05 | w    |  |  |  |

| Maximum output power dissipation              | 2.2nF capacitor                                         | -   | 1.09 |      |  |  |  |

|                                               | SOW-8                                                   |     |      |      |  |  |  |

| Maximum power dissipation on input and output | V <sub>CC1</sub> =15V, V <sub>CC2</sub> =15V, f=1.9MHz, | -   | 1.04 |      |  |  |  |

| Maximum input power dissipation               | 50% duty cycle, square wave,                            | -   | 0.05 | W    |  |  |  |

| Maximum output power dissipation              | 2.2nF load capacitor                                    | -   | 0.99 |      |  |  |  |

## 7.5 Electrical Characteristics

$T_A \!\!=\!\! -40 \!\!\sim\!\! 125 ^{\circ} \! C$  ,  $V_{CC1} \!\!=\!\! 3.3$  or 5V,  $V_{CC2} \!\!=\!\! 15 V$ ,  $C_L{}^{(1)} \!\!=\!\! 100 pF$ .

Output pin: current towards outside of the chip is positive direction; Input pin: current towards inside of the chip is positive direction.

| SYMBOL                | PARAMETER                                         | TEST CONDITIONS                              | MIN                   | TYP                   | MAX                  | UNIT |

|-----------------------|---------------------------------------------------|----------------------------------------------|-----------------------|-----------------------|----------------------|------|

|                       | SUPPLY                                            | CURRENTS                                     | l                     |                       |                      |      |

| I <sub>VCC1</sub>     | Input supply quiescent current                    | -                                            | -                     | 1.4                   | 2.4                  | Λ    |

| I <sub>VCC2</sub>     | Output supply quiescent current                   | -                                            | -                     | 1.3                   | 1.8                  | mA   |

|                       | SUPPLY VOLTAGE UND                                | ERVOLTAGE THRESHO                            | LDS                   |                       |                      | •    |

| V <sub>ON1</sub>      | VCC1-GND1 Positive-going UVLO threshold voltage   | -                                            | -                     | 2.6                   | 2.8                  |      |

| V <sub>OFF1</sub>     | VCC1-GND1 Negative-going UVLO threshold voltage   | -                                            | 2.4                   | 2.5                   | -                    | V    |

| V <sub>UV, HYS1</sub> | VCC1-GND1 UVLO threshold hysteresis               | -                                            | -                     | 0.1                   | -                    | ]    |

|                       | UVLO THRESH                                       | OLDS BTD5350xCx                              |                       |                       |                      |      |

| V <sub>ON2</sub>      | VCC2-VEE2 Positive-going UVLO threshold voltage   | -                                            | -                     | 12                    | 13                   |      |

| V <sub>OFF2</sub>     | VCC2-VEE2 Negative-going UVLO threshold voltage   | -                                            | 10.3                  | 11                    | -                    | V    |

| V <sub>UV, HYS2</sub> | VCC2-VEE2 UVLO threshold voltage hysteresis       | -                                            | -                     | 1                     | -                    |      |

|                       | UVLO THRESH                                       | OLDS BTD5350xBx                              |                       |                       |                      | •    |

| V <sub>ON2</sub>      | VCC2-VEE2 Positive-going UVLO threshold voltage   | -                                            | -                     | 8.7                   | 9.4                  |      |

| V <sub>OFF2</sub>     | VCC2-VEE2 Negative-going UVLO threshold voltage   | -                                            | 7.3                   | 8                     | -                    | V    |

| V <sub>UV, HYS2</sub> | VCC2-VEE2 UVLO threshold voltage hysteresis       | -                                            | -                     | 0.7                   | -                    |      |

|                       | LO                                                | GIC I/O                                      |                       |                       |                      | •    |

| V <sub>IH</sub>       | Positive-going input threshold voltage (IN+, IN-) | -                                            | -                     | 0.55×V <sub>CC1</sub> | 0.7×V <sub>CC1</sub> |      |

| VIL                   | Negative-going input threshold voltage (IN+, IN-) | -                                            | 0.35×V <sub>CC1</sub> | 0.45×V <sub>CC1</sub> | -                    | V    |

| V <sub>IN, HYS</sub>  | Input Hysteresis voltage                          | -                                            | -                     | 0.1×V <sub>CC1</sub>  | -                    | 1    |

| I <sub>IH</sub>       | High-level input leakage at IN+                   | IN+=V <sub>CC1</sub>                         | -                     | 160                   | 240                  |      |

|                       | Lavulavel input leel are at INI                   | IN-=GND1                                     | -240                  | -160                  | -                    | μΑ   |

| I <sub>IL</sub>       | Low-level input leakage at IN-                    | IN-=GND1-5V                                  | -310                  | -100                  | -                    |      |

|                       | GATE DF                                           | RIVER STAGE                                  |                       |                       |                      | •    |

| Іон                   | Peak source current                               | IN+=HIGH, IN-=LOW                            | 5                     | 10                    | -                    | _    |

| loL                   | Peak sink current                                 | IN+=LOW, IN-=HIGH                            | 5                     | 10                    | -                    | A    |

| Vон                   | High level output voltage VCC2-OUT or VCC2-OUTH   | I <sub>OUT</sub> =+20mA<br>IN+=HIGH, IN-=LOW | -                     | 60                    | -                    | mV   |

| Vol                   | Low level output voltage OUT-VEE2 or OUTL-VEE2    | I <sub>OUT</sub> =-20mA<br>IN+=LOW, IN-=HIGH | 5                     | 7                     | -                    | mV   |

|                       | 1                                                 | <u>.</u>                                     |                       |                       |                      |      |

#### (Continued)

|                        |                                           | MI                    | LLER CLAMP BTD5350Mx                                                                            |     |     |     |       |

|------------------------|-------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| $V_{clamp}$            | Low-level clamp voltage                   |                       | I <sub>clamp</sub> =20mA                                                                        | -   | 7   | 10  | mV    |

| I <sub>clamp</sub>     | Low-level clamp current                   |                       | V <sub>CLAMP</sub> =VEEx+15V                                                                    | 5   | 10  | -   | А     |

| V <sub>clamp-TH</sub>  | Clamping threshold volta                  | ge                    | -                                                                                               | -   | 2.2 | -   | V     |

|                        |                                           | SH                    | IORT-CIRCUIT CLAMPING                                                                           |     |     |     |       |

|                        | Clamping voltage<br>(OUT-VCC2 or OUTH-VCC | 2)                    | IN+=HIGH, IN-=LOW, t <sub>CLAMP</sub> =10μs,<br>I <sub>OUTH</sub> or I <sub>OUT</sub> =500mA    | -   | 1   | 1.3 |       |

| V <sub>CLP-OUT</sub>   | Clamping voltage (VEE2-OUT or VEE2-OUT    | or VEE2-CLAMP)        | IN+=LOW, IN-=HIGH, t <sub>CLAMP</sub> =10µs,<br>I <sub>CLAMP</sub> or I <sub>OUTL</sub> =-500mA | -   | 1.5 | -   | V     |

|                        | (VELZ GOT OF VELZ GOTE OF VELZ GERWIT)    |                       | IN+=LOW, IN-=HIGH, ICLAMP OR IOUTL=-20mA                                                        | -   | 0.9 | 1   | ]     |

|                        |                                           | ACTI                  | VE PULL-DOWN FUNCTION                                                                           |     |     |     |       |

| V <sub>OUTSD</sub>     | Active pulldown voltage of CLAMP, OUT     | on OUTL,              | l <sub>OUT</sub> =-1A (sinking into OUT,<br>OUTL or CLAMP pin), VCC2=left open                  | -   | 2.3 | 2.6 | V     |

|                        |                                           | SI                    | WITCHING PARAMETERS                                                                             | •   |     |     |       |

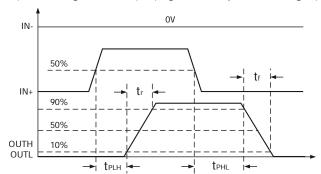

| t <sub>PLH</sub>       | Propagation delay, high                   |                       | C <sub>L</sub> =100pF                                                                           | -   | 60  | 75  |       |

| t <sub>PHL</sub>       | Propagation delay, low                    |                       | C <sub>L</sub> =100pF                                                                           | -   | 60  | 75  | 1     |

| tr                     | Output-signal rise time                   |                       | C <sub>L</sub> =1nF                                                                             | -   | 10  | 26  | ]     |

| t <sub>f</sub>         | Output-signal fall time                   |                       | C <sub>L</sub> =1nF                                                                             | -   | 10  | 26  | ns    |

| t <sub>PWD</sub>       | Pulse width distortion[tph                | ıL-t <sub>PLH</sub> ] | C <sub>L</sub> =100pF                                                                           | -   | 1   | 20  | ]     |

| t <sub>sk</sub> 2)     | Part-to-part skew                         |                       | C <sub>L</sub> =100pF                                                                           | -   | 1   | 25  | ]     |

| t <sub>UVLO1-rec</sub> | Undervoltage lockout                      | Input side            | VCC1                                                                                            | -   | 50  | -   |       |

| t <sub>UVLO2-rec</sub> | recovery delay time                       | Output side           | VCC2                                                                                            | -   | 50  | -   | μs    |

| CMTI                   | Common-mode transien                      | t immunity            | INx tied to GND or VCC1, V <sub>CM</sub> =1500V                                                 | 100 | 150 | -   | kV/μs |

## 7.6 Insulation Specifications

#### 7.6.1 SOP-8 Safety Parameters

| SYMBOL            | PARAMETER                                 | TEST CONDITIONS                                                                        | MIN    | TYP | MAX | UNIT            |

|-------------------|-------------------------------------------|----------------------------------------------------------------------------------------|--------|-----|-----|-----------------|

| CLR               | External Clearance                        | -                                                                                      | 4      | -   | -   | mm              |

| CPG               | External Creepage                         | -                                                                                      | 4      | -   | -   | mm              |

| DTI               | Distance through the insulation           | -                                                                                      | 17     | -   | -   | μm              |

| CTI               | Comparative tracking index                | DIN EN 60112                                                                           | 600    | -   | -   | V               |

|                   | Overveltage category per IEC 60664.1      | Rated mains voltage ≤ 150Vrms                                                          | I-IV   | -   | -   |                 |

|                   | Overvoltage category per IEC 60664-1      | Rated mains voltage ≤ 300Vrms                                                          | I- III | -   | -   | -               |

|                   |                                           | DIN V VDE 0884-11                                                                      |        |     | ,   | ,               |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage | AC voltage (bipolar)                                                                   | 990    | -   | -   | V <sub>PK</sub> |

| V <sub>IOWM</sub> | Maximum isolation working voltage         | AC voltage (sine wave); time dependent dielectric breakdown (TDDB) test                | 700    | -   | -   | Vrms            |

| V <sub>IOTM</sub> | Maximum transient isolation voltage       | 100% V <sub>ІОТМ</sub> , 60s; 120% V <sub>ІОТМ</sub> , 1s                              | 4242   | -   | -   | V <sub>PK</sub> |

| V <sub>IOSM</sub> | Maximum surge isolation voltage           | IEC 62368-1, 1.2/50μs waveform, 1.6V <sub>IOSM</sub>                                   | 4242   | -   | -   | VPK             |

|                   |                                           | Method a:V <sub>IN</sub> =V <sub>IOTM</sub> , 60s; Vpd=1.2 V <sub>IOTM</sub> , 10s     | -      | -   | 5   |                 |

| q <sub>pd</sub>   | Apparent charge                           | Method a:V <sub>IN</sub> =V <sub>IOTM</sub> , 60s; Vpd=1.6 V <sub>IOTM</sub> , 10s     | -      | -   | 5   | рС              |

|                   |                                           | Method b1:V <sub>IN</sub> =1.2V <sub>IOTM</sub> , 1s; Vpd=1.875 V <sub>IOTM</sub> , 1s | -      | -   | 5   |                 |

| Cıo               | Barrier capacitance, input to output      | V₀=0.4Vpk, f=1MHz, sine wave                                                           | -      | 1.2 | -   | pF              |

Note: 1. C<sub>L</sub>: Load capacitance from output pin OUTx to VEE2 or GND2.

2. t<sub>sk</sub> is the magnitude of the difference in propagation delay times between the output of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals and loads guaranteed by characterization.

#### (Continued)

|                  | Isolation resistance, input to output | Test voltage of 500V, T <sub>A</sub> =25°C              | 10 <sup>12</sup> | .012 |   |      |

|------------------|---------------------------------------|---------------------------------------------------------|------------------|------|---|------|

| Rio              |                                       | Test voltage of 500V, 100°C < T <sub>A</sub> < 125°C    | 1011             | -    | - | Ω    |

|                  |                                       | Test voltage of 500V, T <sub>s</sub> =150°C             | 10 <sup>9</sup>  | -    | - |      |

|                  | Pollution degree                      | -                                                       | 1                | 2    | - | -    |

| UL1577           |                                       |                                                         |                  |      |   |      |

| V <sub>ISO</sub> | Withstand isolation voltage           | 100% V <sub>ISO</sub> , 60s; 120% V <sub>ISO</sub> , 1s | 3000             | -    | - | Vrms |

## 7.6.2 SOW-8 Safety Parameters

| SYMBOL            | PARAMETER                                 | TEST CONDITIONS                                                                        | MIN             | TYP | MAX  | UNIT            |  |

|-------------------|-------------------------------------------|----------------------------------------------------------------------------------------|-----------------|-----|------|-----------------|--|

| CLR               | External Clearance -                      |                                                                                        | 8.5             | -   | -    |                 |  |

| CPG               | External Creepage                         | -                                                                                      | 8.5             | -   | -    | mm              |  |

| DTI               | Distance through the insulation           | -                                                                                      | 17              | -   | -    | - μm            |  |

| CTI               | Comparative tracking index                | DIN EN 60112                                                                           | 600             | -   | -    | V               |  |

|                   | Overvoltage category per IEC 60664-1      | Rated mains voltage < 600Vrms                                                          | 1-111           | -   | -    |                 |  |

|                   |                                           | Rated mains voltage < 1000Vrms                                                         | 1-11            | -   | -    | -               |  |

|                   |                                           | DIN V VDE 0884-11                                                                      |                 | J.  |      | Į.              |  |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage | AC voltage (bipolar)                                                                   | 2121            | -   | -    | V <sub>PK</sub> |  |

| $V_{\text{IOWM}}$ | Maximum isolation working voltage         | AC voltage (sine wave); time dependent dielectric breakdown (TDDB) test                | 1500            | -   | Vrms |                 |  |

| V <sub>IOTM</sub> | Maximum transient isolation voltage       | 100% V <sub>ЮТМ</sub> , 60s; 120% V <sub>ЮТМ</sub> , 1s                                | 7000            | -   | -    |                 |  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage           | IEC 62368-1, 1.2/50μs waveform, 1.6 x V <sub>IOSM</sub>                                | 8000            | -   | -    | V <sub>PK</sub> |  |

|                   |                                           | Method a:V <sub>IN</sub> =V <sub>IOTM</sub> , 60s; Vpd=1.2 V <sub>IOTM</sub> , 10s     | -               | -   | 5    |                 |  |

| $q_{pd}$          | Apparent charge                           | Method a:V <sub>IN</sub> =V <sub>IOTM</sub> , 60s; Vpd=1.6 V <sub>IOTM</sub> , 10s     | -               | -   | 5    | рС              |  |

|                   |                                           | Method b1:V <sub>IN</sub> =1.2V <sub>IOTM</sub> , 1s; Vpd=1.875 V <sub>IOTM</sub> , 1s | -               | -   | 5    |                 |  |

| C <sub>IO</sub>   | Barrier capacitance, input to output      | V <sub>IO</sub> =0.4Vpk, f=1MHz, sine wave                                             | -               | 1.2 | -    | pF              |  |

| Rio               | Isolation resistance, input to output     | Test voltage of 500V, T <sub>A</sub> =25°C                                             | 1012            | -   | -    | Ω               |  |

|                   |                                           | Test voltage of 500V, 100°C < T <sub>A</sub> < 125°C                                   | 1011            | -   | -    |                 |  |

|                   |                                           | Test voltage of 500V, T₅=150°C                                                         | 10 <sup>9</sup> | -   | -    |                 |  |

|                   | Pollution degree                          | -                                                                                      | -               | 2   | -    | -               |  |

|                   | 1                                         | UL1577                                                                                 |                 | 1   | 1    |                 |  |

| V <sub>ISO</sub>  | Withstand isolation voltage               | 100% V <sub>ISO</sub> , 60s; 120% V <sub>ISO</sub> , 1s                                | 5000            | -   | -    | Vrm             |  |

|                   | l .                                       | l .                                                                                    |                 |     |      | 1               |  |

## 8. Parameter Testing

### 8.1 Propagation Delay

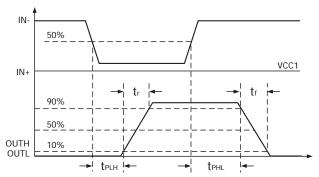

The method for measuring the rise time  $(t_r)$  and fall time  $(t_f)$ : the propagation delay OUTH and OUTL for non-inverting input (see Figure 1); the propagation delay for inverting input (see Figure 2).

Figure 1. Input and Output Propagation Delay (Non-Inverting Configuration)

Figure 2. Input and Output Propagation Delay (Inverting Configuration)

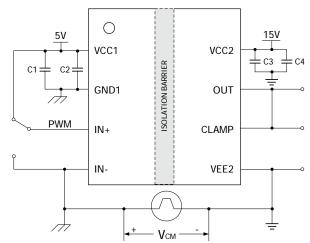

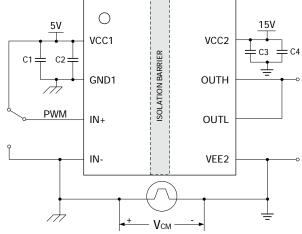

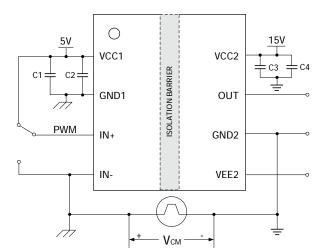

#### **8.2 CMTI**

Figure 3. CMTI Test Circuit for BTD5350Mx

Figure 4. CMTI Test Circuit for BTD5350Sx

Figure 5. CMTI Test Circuit for BTD5350Ex

## 9. Function Description

### 9.1 Isolation Design Description

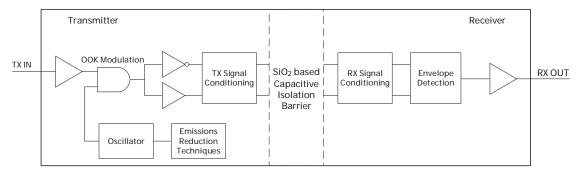

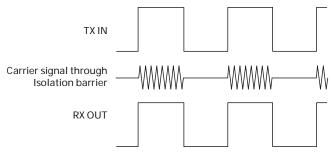

The isolation inside the BTD5350x series is implemented with high voltage SiO2 based capacitors. There is a capacitor on each of the primary-side and secondary-side to enhance insulation. The signal across the isolation has an on-off keying (OOK) modulation scheme to transmit the digital data. The primary-side transmits a high-frequency carrier to represent one digital state, and sends no signal to represent the other digital state. On the secondary side, the receiver demodulates the signal and produces output for control. One can also add special anti-jamming circuit on the primary /secondary sides to enhance the CMTI performance and minimize the radiate emissions (see Figure 6, 7).

Figure 6. Conceptual Block Diagram of a Capacitive Data Channel

Figure 7. OOK Based Modulation Scheme

#### 9.2 Input Stage Characteristics

With input pins and secondary side completely isolated, BTD5350 is designed to be CMOS-compatible. It supports 3.3V, 5V and 15V level input, making the chip easy to accept control of multiple logic levels. It also has a Internal integrated filter circuit with  $0.1^*$  VCC1 hysteresis for improving noise immunity of the input stage. The IN+ input port has a  $128k\Omega$  pull-down resistor to force it grounding, the IN- input port has a  $128k\Omega$  pull-up resistor to make it go high to the power supply, which can ensure that the output ports are in OFF state when input ports are left open. However, in order to configure the initial power-on state of the driver IC, Bronze Technologies still recommends adding externally an appropriate pull-up or pull-down resistor to the input.

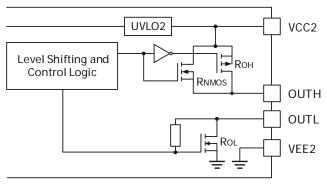

### 9.3 Output Booster Characteristics

The BTD5350x has a rail-to-rail push stage output. The pull-up structure of the output stage consists of a P-channel MOSFET and an N-channel MOSFET connected in parallel. At turn-on, N-channel MOSFET provides high current driving capability. P-channel MOSFET provides a small steady-state conduction voltage drop during steady conduction. The pull-down structure is implemented using an N-channel MOSFET. A  $1M\Omega$  resistor is connected in parallel between the drain and gate of the MOSFET to effectively clamp the gate voltage of the power device in the event of a loss of power on the chip to prevent the occurrence of partial turn-on. However, in order to ensure reliable shutdown of the power device, Bronze Technologies recommends that appropriate pull-down resistor be added to the gate.

In order to prevent the output port voltage from overvoltage/overcurrent damage when the positive secondary-side power supply voltage VCC2 becomes lower than the negative secondary-side power supply voltage VEE2, due to gate oscillation on output terminals, the 5350M version is designed with a Miller clamp on the output port to effectively suppress oscillations. However, to ensure the normal operation of the drive circuit, Bronze Technologies recommends to use Schottky diodes at the gate to clamp the positive and negative power supplies respectively.

Figure 8. Output Stage

#### 9.4 Protection Functions

#### 9.4.1 Undervoltage Lockout

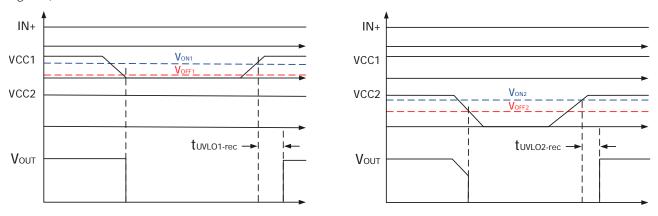

The BTD5350x has undervoltage lockout (UVLO) function on the primary-side power supply and the secondary-side total supply voltage to prevent the gate drive voltage from being insufficient. When the supply voltage drops below UVLO threshold, the ASIC turns off the output to protect the power devices. When the supply voltage reaches the positive-going negative-going threshold, the ASIC resumes the output. To prevent repeated action near the UVLO threshold, the ASIC is configured with hysteresis. In order to avoid the uncertainty of the output state after power-on, the ASIC first enters an UVLO state after power-on, keeps the output off until the supply voltage is established and then starts normal operation (see Figure 9).

Figure 9. UVLO Functions

#### 9.4.2 Miller Clamp

The active Miller clamp function is used to prevent the power devices from false turn-on of the power switched cause by the Miller current. A low impedance path is added between the gate terminal and ground (VEE2) to sink the Miller current. The Miller clamp function clamps the gate voltage of the power device to less than 2V when the output is in the off state.

#### 9.4.3 Short-Circuit Clamping

In short-circuit conditions, the gate voltage of the power devices tend to rise, so the short-circuit clamping function is used to clamp its gate voltage. The short-circuit clamping function helps protect the IGBT or MOSFET gates from overvoltage breakdown or degradation. The short circuit clamping function is implemented by adding a diode between the OUT, OUTL or CLAMP pins and the VCC2 pins inside the driver. The internal diode can carry a current up to 500 mA for  $10 \mu \text{s}$  or a continuous current of 20 mA. Use external Schottky diodes to improve current conduction capability as needed.

#### 9.4.4 Active Pull-Down

The active pull-down function is used to pull the IGBT or MOSFET gate to the low state when no power is connected to the VCC2. This feature prevents false IGBT and MOSFET turn-on on the OUT, OUTL and CLAMP pins by clamping the output to approximately 2V.

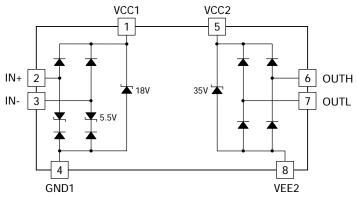

#### 9.5 ESD Structure

The figure below shows the ESD-protected diode configuration of the input and output pins.

Figure 10. ESD Structure Diagram

#### 9.6 Truth Table

#### BTD5350M and BTD5350E

| IN+ | IN- | VCC1                                      | VCC2                            | OUT |

|-----|-----|-------------------------------------------|---------------------------------|-----|

| Х   | Х   | <uvlo< td=""><td>Х</td><td>L</td></uvlo<> | Х                               | L   |

| Х   | Х   | Х                                         | <uvlo< td=""><td>L</td></uvlo<> | L   |

| Н   | L   | >UVLO                                     | >UVLO                           | Н   |

| Н   | Н   | >UVLO                                     | >UVLO                           | L   |

| Ĺ   | L   | >UVLO                                     | >UVLO                           | L   |

| L   | Н   | >UVLO                                     | >UVLO                           | L   |

#### BTD5350S

| IN+ | IN- | VCC1                                                   | VCC2                                         | OUTH | OUTL |

|-----|-----|--------------------------------------------------------|----------------------------------------------|------|------|

| Х   | Х   | <uvlo< td=""><td>X</td><td>Hi-Z</td><td>L</td></uvlo<> | X                                            | Hi-Z | L    |

| Х   | Х   | Х                                                      | <uvlo< td=""><td>Hi-Z</td><td>L</td></uvlo<> | Hi-Z | L    |

| Н   | L   | >UVLO                                                  | >UVLO                                        | Н    | Hi-Z |

| Н   | Н   | >UVLO                                                  | >UVLO                                        | Hi-Z | L    |

| L   | L   | >UVLO                                                  | >UVLO                                        | Hi-Z | L    |

| L   | Н   | >UVLO                                                  | >UVLO                                        | Hi-Z | L    |

## 10.Applications

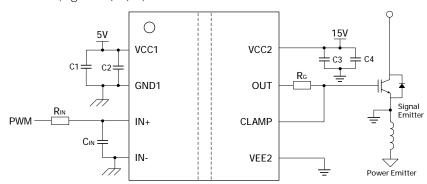

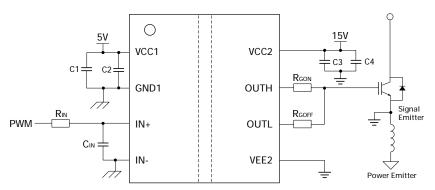

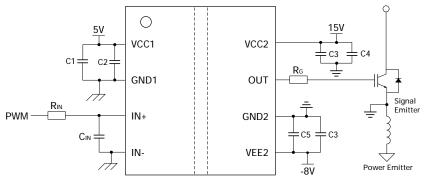

The following sections introduce the basic typical application of Bronze Technologies driver ICs, which is for reference only. In practical application, users need to verify and test its applicability according to their own design requirements to confirm the system functions.

### **10.1 Typical Applications**

Bronze Technologies recommends that customers add a RC filter with a small time constant at the input port to filter out high-frequency interference without adding a large delay. It is recommended that the resistance value should be between 0 and  $100\Omega$  and the capacitance should be less than 1000pF. When setting this parameter, the influence between high frequency interference and delay needs to be taken into account.

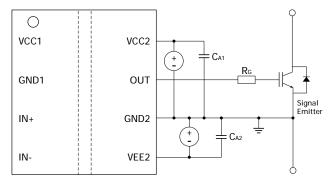

To ensure the supply stability, Bronze Technologies recommends to add appropriate blocking capacitor between the power supply and ground. It is recommended to parallel a 1uF+ 0.1uF capacitor between VCC1-GND1, and a 10uF+ 0.22uF capacitor between VCC2-VEE2 (Figure 11,12,13).

Figure 11. Typical Application Circuit for BTD5350M

Figure 12. Typical Application Circuit for BTD5350S

Figure 13. Typical Application Circuit for BTD5350E

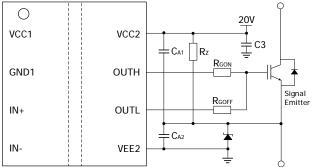

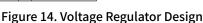

### 10.2 Recommended Design Of Secondary Side Supply

In order to avoid false turn-on of the gate of the power device due to interference, it is recommended that customers add a negative power supply when designing the driving output. It is recommended to use the following two methods to generate the negative supply: use a regulator to generate stable negative voltage (see Figure 14); or use both positive and negative supplies (see Figure 15).

Figure 15. Dual-Supply Design

## 11. Packaging and Packing Information

## 11.1 Package Identifier

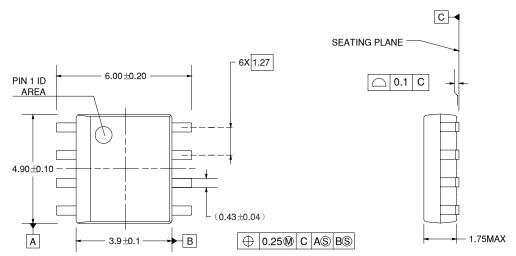

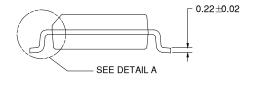

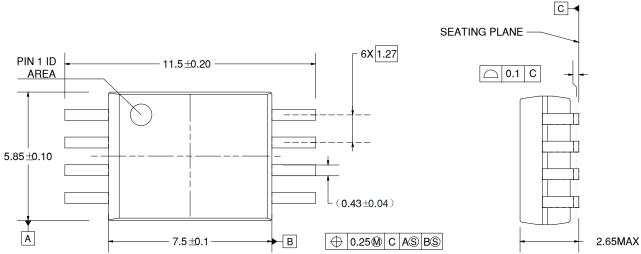

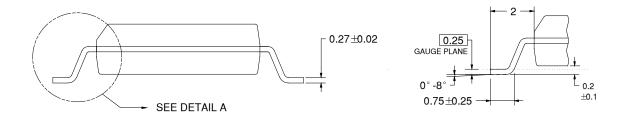

### 11.1.1 SOP-8 Package Identifier

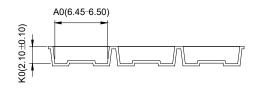

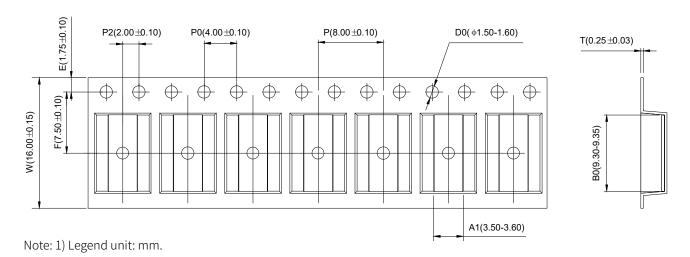

Note: 1) Legend unit: mm.

#### 11.1.2 SOW-8 Package Identifier

Note: 1) Legend unit: mm.

#### **Electrostatic Discharge Caution**

This integrated circuit can be damaged by ESD. Bronze recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

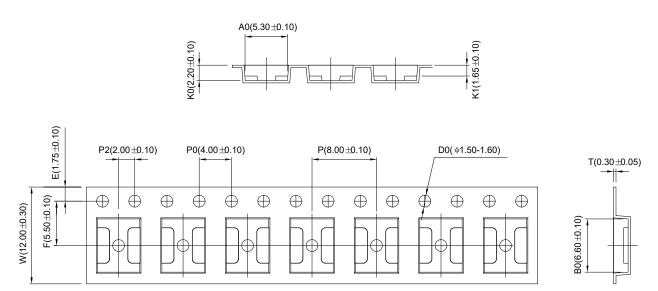

## 11.2 Packing Information

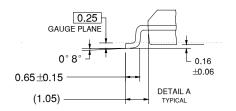

## 11.2.1 SOP-8 Packing Information

Note: 1) Legend unit: mm.

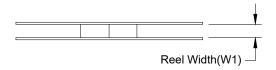

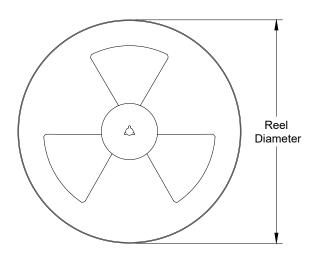

#### **REEL DIMENSIONS**

| ITEM           | FOOTPRINT |

|----------------|-----------|

| Reel Diameter  | 13 inches |

| Reel Width(W1) | 12.4mm    |

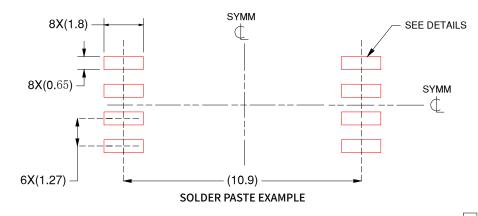

#### 11.2.2 SOW-8 Packing Information

## **REEL DIMENSIONS**

| ITEM           | FOOTPRINT |  |  |

|----------------|-----------|--|--|

| Reel Diameter  | 13 inches |  |  |

| Reel Width(W1) | 16.4mm    |  |  |

### 12. Version Description

| REVISION | SION NOTES                      |             |

|----------|---------------------------------|-------------|

| Rev.0.0  | Released datasheet              | 04-Jan-2023 |

| Rev.0.1  | Figures and description updated | 28-Nov-2023 |

#### IMPORTANT NOTICE AND DISCLAIMER

Bronze provides technical and reliability data(including datasheets), design resources(including 3D model, reference designs), application or other design advice, tools, safety information, and with all faults, and disclaims all warranties. Express and implied, including without limitation any implied warranties of merchantability, fitness for a particular purpose or non-infringement of third party intellectual property rights.

These resources are intended for skilled developers designing with bronze products. You are solely responsible for

- (1) selecting the appropriate bronze products for your application

- (2) designing, validating and testing your application

- (3) ensuring your application meets applicable standards.

Bronze reserves the right to modify data, texts and materials at any time, these resources are subject to change without notice. Please visit the bronze website <a href="www.qtjtec.com">www.qtjtec.com</a> account for the latest information. Bronze grants you permission to use these resources only for development of an application that uses the bronze products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other bronze intellectual property right or to any third party intellectual property right. For any claims, damages, losses and costs arising from using of these resources,

bronze disclaims responsibility for, and you will fully indemnify bronze and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. And bronze have the right to recover losses caused by infringement of intellectual property rights.

#### Bronze Technology Group | Shenzhen bronze Technology Co., Ltd

- © Shenzhen bronze Technology Co., Ltd

- www.qtjtec.com

- **☎** +86 0755 33379866

- support@qtjtec.com